良好的PCB布局如何帮助你更快的制作高质量电路板

发表时间:2021-10-04 10:00:00 人气:2913

商业应用利用从3 MHz到30 GHz以上的高频带。其中包括电视,FM收音机,射电天文学,手机,Wi-Fi等。上述应用中的各种产品都使用高频印刷电路板(PCB)。PCB的低生产成本使其对现代电子设备制造商具有吸引力。但是,数量较少时,每块板的价格可能会更高。

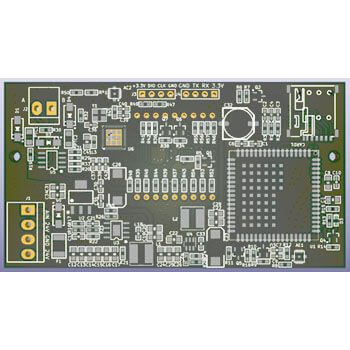

为了获得更好,更快的PCB,设计人员在设计电路板时需要注意三个主要领域:建筑材料,组件互连和走线布局。

建筑材料

在PCB的设计过程中,设计人员主要考虑PCB材料的两个主要特征。其中之一是介电常数,另一个是损耗角正切。介电常数会影响信号通过电路板的速度。损耗角正切是指由于材料内的吸收而丢失的信号量。尽管FR4是用于构造低频电路的常用材料,但对于使用频率超过1 GHz的那些,仍需要更多优质材料。

组件互动

对于高频板的设计者来说,考虑元件与PCB之间的连接点非常重要。例如,将焊盘放置在接地平面上可以充当电容器。表面贴装器件(SMD)的使用具有较小的结构特征和引线长度,因此可以在很大程度上解决该问题。但是,随着频率的增加,包括SMD形式在内的无源元件可能具有非理想特性。设计人员必须考虑到这一点并补偿这些特性。

迹线布局

一旦设计师令人满意地确定了建筑材料和组件的选择,他/她就必须以在低功率环境下实现高速运行为目标。这涉及:

●最小化车载噪声的产生

●最小化走线之间的串扰

●减少地面反弹的影响

●阻抗匹配

●正确的信号线端接

最小化噪声的产生

减少噪声有两个主要方面。其中之一是整个板上的电源分配,另一个涉及电源噪声过滤。

为了在整个PCB上分配电源,设计人员可以使用电源平面或电源总线网络。通常,多层PCB上的电源层由两个或多个将Vcc和GND承载到设备的金属层组成。由于电源平面几乎覆盖了PCB的整个区域,因此这些平面的DC电阻较低。因此,电源平面在将Vcc电平平均分配给所有设备的同时使其保持恒定。它还提供了噪声保护,极高的电流吸收能力以及对PCB承载的信号的良好屏蔽。

电源平面的替代方案是电源总线,该电源总线由两个或多个将Vcc和GND承载到设备的宽金属走线组成。由于这种方法比电源平面便宜,因此两层PCB经常使用它们。使用电源总线网络进行设计时,设计人员需要确保走线宽度尽可能宽。但是,与电源平面相比,电源总线网络的直流电阻要低得多。

分离承载模拟和数字电源的平面和电源总线有助于最大程度地减少机载噪声的产生,因为这会阻止两者之间的相互作用。但是,全数字系统可能没有单独的模拟电源平面,添加新的电源平面可能变得非常昂贵,除非设计人员在现有层上创建了分区的岛或分离平面。

虽然建议在系统上的模拟电源和数字电源之间分开这些平面,但在两种电路类型之间仍可能存在一些不必要的相互作用。以下建议可能有助于减少噪声的产生:

●通过为模拟电源使用单独的电源板来平均分配电源。请勿使用走线或多个信号层布线电源。

●在电源平面附近使用接地平面通常有助于减少电源产生的噪声。

●仅将模拟组件放置在模拟接地平面上,将数字组件放置在数字接地平面上。

●使用铁氧体磁珠将模拟电源线与数字电源线隔离。

最小化迹线之间的交互

平行走线之间信号的不必要耦合会导致串扰。设计人员通过适当的布线,并在层堆叠中使用微带线和带状线布局,将串扰降至最低。

当被迫使用彼此相邻的两个信号层时,设计人员通过将一层中的所有走线都与下一层中的走线成角度地布线,从而将串扰降至最低。他们为使串扰最小化而采用的其他技术是使信号层与其相邻平面之间的距离最小化,以及增加两个信号层之间的距离。

以下建议可帮助设计人员减少带状线或微带线布局中的串扰:

保持信号线之间的最大空间-尽可能地限制布线。一般的经验法则是将信号线间隔至少三倍于电介质高度或四倍于走线宽度。

保持传输线的导体尽可能靠近其接地平面,以使其紧密耦合至接地平面,并将其与相邻信号去耦。

关键网络可以通过使用差分路由技术受益。这可能需要匹配每个迹线的长度和回转度。

对于实质性的耦合,可能有助于在不同的层上路由相互垂直的单个信号。

对于单端信号,最小化并行游程长度有助于减少串扰。使用短的并行部分进行布线,并避免走线之间的长耦合部分。

如果无法更改两条走线之间的间距,则将走线与接地层之间的距离减小到10密耳以下可以帮助减少串扰。

减少地面反弹的影响

使用更快的数字设备并减少输出切换时间,设备输出会在释放负载电容时表现出更高的瞬态电流。另外,可能有一个设备的多个输出同时从逻辑高切换到逻辑低。同时向地下倾倒电流可能会暂时升高地面的电势,导致基准发生变化,这种现象就是地面反弹。影响接地弹跳的主要条件包括负载电容,插座电感和同时开关输出的数量。

设计人员通过以下设计方法来减少地面反弹:

●将过孔放置在电容器焊盘附近,或在它们之间使用短而宽的走线

●使用从电源引脚到电源平面,孤岛或去耦电容器的宽和短走线。这通过降低串联电感来减小接地反弹的可能性,并且瞬态电压从电源引脚到电源层下降。

●将每个接地引脚或过孔分别连接到接地层。菊花链导致共享接地路径,从而增加了回路电流回路的电阻和电感

●按照IC制造商的建议添加去耦电容器。去耦电容必须尽可能靠近设备的电源和接地引脚。

●将开关输出移至尽可能靠近封装接地引脚的位置

●避免上拉电阻,而使用更多的下拉电阻

●使用具有单独的Vcc和GND平面的多层PCB,从而利用Vcc-GND平面的本征电容

●使用同步设计,因为这些不受同步开关引脚的影响

●接地引脚和电源引脚之间的距离非常近,从而减小了互感,因为两个引脚的电流方向相反。

●通过在电容器焊盘上使用更大的过孔尺寸来最小化去耦电容器中的电感

●通过使用表面贴装电容器来最小化引线电感

●使用有效串联电阻较低的电容器

阻抗匹配和正确的信号线端接

沿着不匹配的阻抗线来回反射的信号会在负载接收器处产生振铃。振铃会导致接收器的误触发,因为它会减小接收器的动态范围。设计人员通过使用适当的信号线端接使源阻抗等于走线阻抗和负载阻抗来消除反射。

为了正确匹配阻抗并终止信号线,设计师可以通过以下方法来确保信号完整性:

●在时钟传输线中不使用过孔,因为过孔会导致阻抗变化并产生反射

●保持笔直。不要使用直角弯曲,而应使用弧形轨迹

●尽可能使用点对点时钟走线,并端接时钟信号以最大程度地减少反射

●使用外部设备缓冲负载并限制负载电容

●在每个开关输出处串联增加10至27欧姆的电阻,以限制电流

●放置合适的终端电阻,并确保传输线和终端之间的阻抗匹配等于线路阻抗

●在参考平面内夹层路由时钟轨迹的层,以最大程度地降低噪声

●将走线长度保持在5 cm以下,将阻抗保持在65 ohms以下,并将金属延迟保持在940 ps以下,将电感值保持在40 nH以下,将走线电容保持在20 pF以下,并将总电容保持在30 pF以下,特别是对于关键的高速布线。

结论

除了选择合适的高频材料外,设计师还可以采用很多更好的PCB布局来使其在高频下正常工作。由于每个PCB都是唯一的,因此必须针对其应用进行定制设计。使用PCB CAD或设计套件软件可以帮助设计人员,因为该软件包提供了广泛的功能。

相关咨询

工厂展示

联系我们

成都子程新辉电子设备有限公司

联系人:文先生

手机:13183865499

QQ:1977780637

地址:成都市金牛区星辉西路2号附1号(台谊民生大厦)407号